RDL形成用レジスト

再配線/RDL形成めっき用フォトレジスト

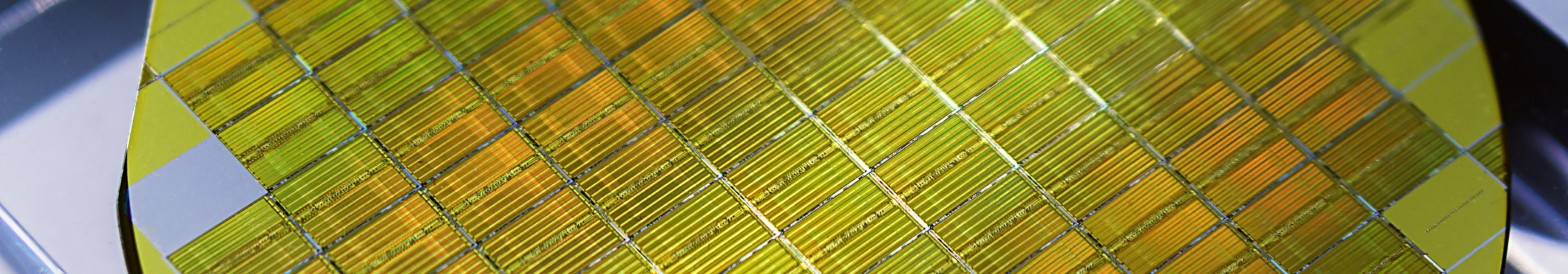

2~20μmの薄膜から厚膜までの各膜厚に応じた再配線形成用めっき対応レジストをご用意しております。最新の高密度半導体パッケージ技術の2.5D/3D半導体実装、TSV - Si貫通電極積層メモリー、WL-CSP ( ウエハレベルチップサイズパッケージ/ Wafer Level Package Chip Size Package )、FOWLP / FOPLP ( Fan Out Wafer-/Panel Level-Package ) 、シリコンインターポーザ―に微細なRDLを形成可能な高解像性、ワイドDOFマージンを有する電解めっき用レジストです。高解像タイプ化学増幅型の両タイプを取り揃えております。

関連技術情報

PMER P-BZシリーズ

8~20μm対応可能な厚膜対応のRDL形成用フォトレジストです。厚膜領域においても矩形の形状が得られます。

特長

- ポジティブトーンタイプ

- 現像液:TMAH 2.38%

- レジスト膜厚: 8μm〜20μm

- ワイドプロセスマージン、良好な剥離性

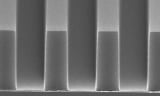

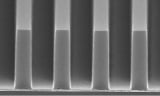

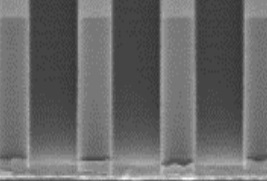

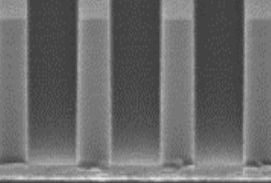

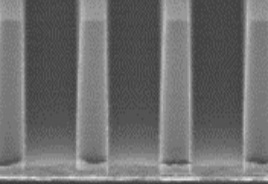

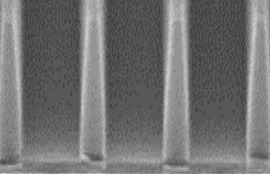

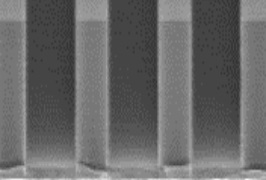

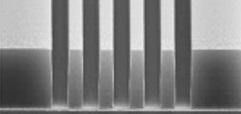

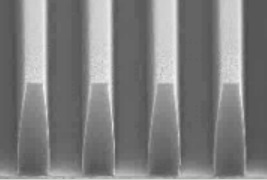

レジストパターン形状

| L/S | 10μm/10μm | 8μm/8μm | 6μm/6μm | 4μm/4μm |

|---|---|---|---|---|

| レジスト膜厚 20μm |

|

|

|

|

条件

下地

Cu

プリベーク

140℃-330秒

露光

ghi 線 ステッパー(NA:0.18)

P.E.B.

100℃-180秒

現像

TMAH 2.38%

60秒 x 2パドル

PMER P-CMシリーズ

超高解像度RDL形成用フォトレジスト。1.5μmパターンを形成し非常にワイドなデフォーカスマージンを有し良好なメッキ液耐性を有するフォトレジストです。

特長

- ポジティブトーンタイプ

- 現像液:TMAH 2.38%

- レジスト膜厚:3μm〜12μm

- 高解像、良好なDOFマージン、良好な剥離性

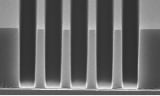

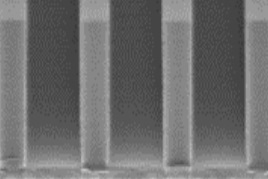

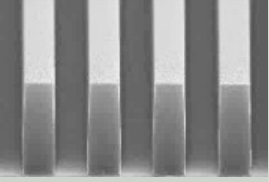

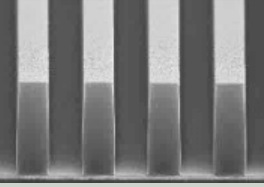

レジストプロファイル

| L/S | 2.0μm/2.0μm | 1.0μm/1.0μm |

|---|---|---|

| レジスト膜厚 5μm |  |

|

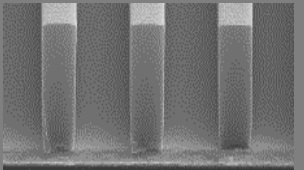

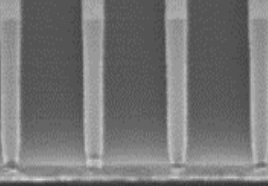

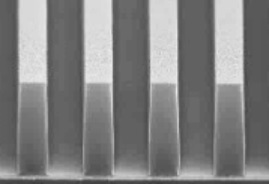

DOF マージン

| レジスト膜厚 6μm センター  |

+4μm | +8μm | +12μm |

|---|---|---|---|

|

|

|

|

| -4μm | -8μm | -12μm | |

|

|

|

条件

下地

Cu

プリベーク

130℃-300秒

露光

i線 ステッパー(NA:0.18), 180mJ/cm2

P.E.B.

100℃-90秒

現像

TMAH 2.38%

30秒 x 2パドル

PMER P-WTシリーズ

超高解像度RDL形成用フォトレジスト。1.5μmパターンを形成し非常にワイドなデフォーカスマージンを有し良好なメッキ液耐性を有するフォトレジストです。

特長

- ポジティブトーンタイプ

- 現像液:TMAH 2.38%

- レジスト膜厚:3μm〜12μm

- 高解像、良好なDOFマージン

- i線、h線の両波長に適用可能

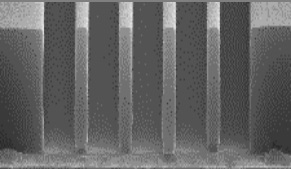

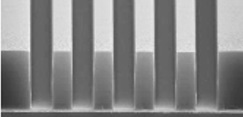

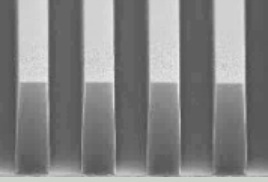

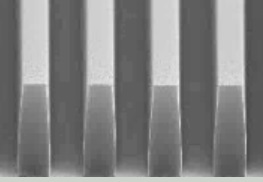

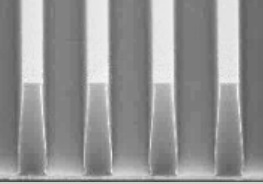

レジストプロファイル

| L/S | 2.0μm/2.0μm | 1.5μm/1.5μm |

|---|---|---|

| レジスト膜厚 6μm |  |

|

DOF マージン

| レジスト膜厚 6μm センター  |

+4μm | +8μm | +12μm |

|---|---|---|---|

|

|

|

|

| -4μm | -8μm | -12μm | |

|

|

|

条件

下地

Cu

プリベーク

130℃-300秒

露光

i線 ステッパー(NA:0.18), 220mJ/cm2

P.E.B.

90℃-240秒

現像

TMAH 2.38%

30秒 x 3パドル

お問い合わせ・資料ダウンロード

ご要望やお困りごとがありましたらお問い合わせください。

各製品に関する資料もダウンロードいただけます。