半導体パッケージ

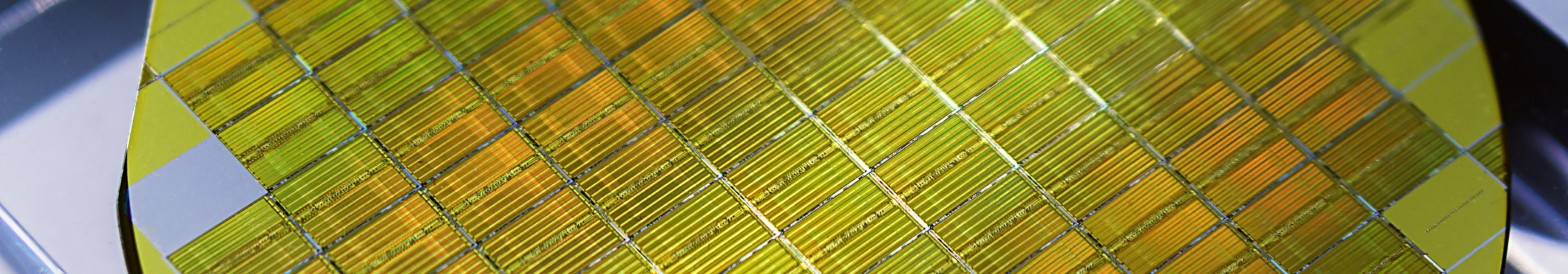

スマートフォンに代表される半導体素子・電子部品が搭載される電子端末製品の高性能化に加え、軽量化/薄型化/小型化への取り組みは、私たちの想像を越えるスピードで進んでいます。この軽量化/薄型化/小型化と省電力、高速通信の実現に極めて重要な役割を果たすのがパッケージ技術です。東京応化工業(tok)では、最先端のパッケージプロセスをはじめ、各種実装プロセスに最適なフォトレジストを開発、製品化しています。パッケージ用フォトレジストとしては、ウエハレベルCSP用/ SiP用/再配線(RDL)用/TAB用/COF用など、広範な生産技術に対応したフォトレジストを提供しています。

半導体の実装(後工程)

Process ワイヤボンディング

パッケージング技術のひとつで、金属の細線ワイヤでリードフレームの金属リードに接続し、通電させる方法です。

金メッキ用レジスト:

LCDドライバー等の金,パラジュウム等貴金属メッキ用 フォトレジスト。

関連製品

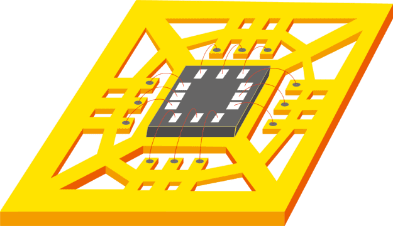

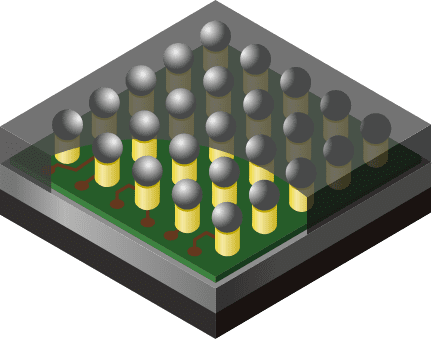

Process ファンアウトパッケージ

バンプと呼ばれる突起状の接続端子を並べて基板と接触させます。当社では、バンプ形成用フォトレジスト、高純度な洗浄液、シンナー、現像液を提供しています。

RDL/再配線 形成:

ウエハレベルパッケージ、ファンアウトパッケージ、インターポーザ―等のRDL形成用フォトレジスト。

関連製品

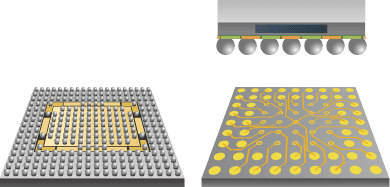

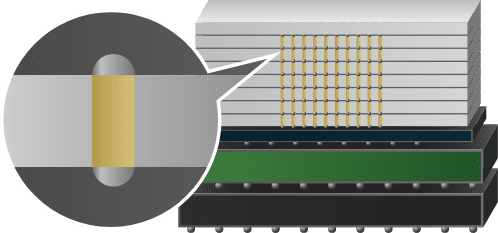

Process TSV

TSVは半導体チップを薄片化して積層し、貫通電極で相互のチップを接続する技術です。当社では、TSV用フォトレジスト、再配線めっき用フォトレジストや接着剤、接着剤専用シンナーを提供しています。

TSV実装:

2.5D、3D 半導体実装のマイクロバンプ、貫通銅電極の形成用メッキ用レジスト, Si 深堀エッチング用高耐熱性厚膜レジスト。

Process Cuピラー ウエハレベルCSP

半導体素子を衝撃や汚染などの外部環境から保護するため、半導体チップを特殊樹脂で固定します。

フリップチップBGAパッケージ用のソルダーバンプ, 銅ピラー電極極形成にメッキ液耐性に優れた厚膜メッキ用レジストです。

関連製品

お問い合わせ・資料ダウンロード

ご要望やお困りごとがありましたらお問い合わせください。

各製品に関する資料もダウンロードいただけます。