技術情報

東京応化工業では、半導体用フォトレジスト事業で培った開発力・対応力・付加価値の高い製品群をベースに新たな分野での需要創出に力を入れています。

詳細をご希望の場合はお気軽にお問い合わせください。多種多様な分野のお客様の開発にお役立ていただければと思います。

技術情報一覧

半導体

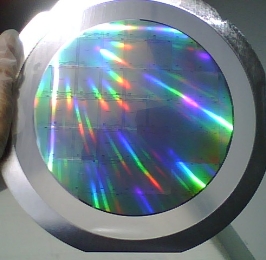

パワー半導体の製造に貢献している

I線用フォトレジスト

1980年代後半に登場したi線用フォトレジスト。微細化ではKrF用フォトレジストに置き換わった現在でも、活躍の場が広がっています。

半導体

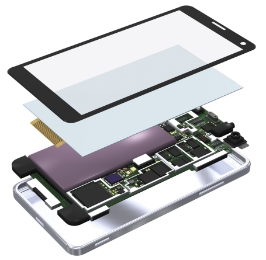

半導体実装

TMMR & TMMFシリーズ

(感光性絶縁材料の開発)

小型・軽量という特徴を活かし、携帯電話などの端末の小型化・高性能化・多機能化に貢献する「SAWフィルタ」について紹介します。

半導体実装

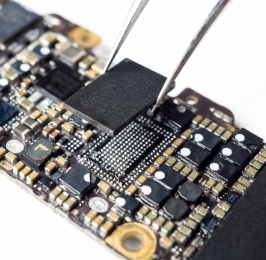

WL-CSP用途向け高速Cu-Pillar

めっき形成材料の開発

スマートフォン用の半導体に採用されている半導体実装技術には当社のパッケージ用フォトレジストが採用されています。その実装技術と当社製品の特長のご説明です。

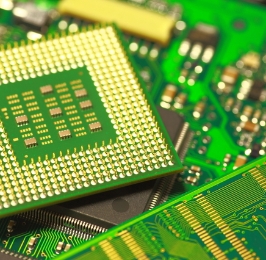

半導体実装

FO(Fan Outの略)パッケージ用途向け

Cu再配線形成材料の開発

チップサイズの制限を受けず、マルチチップ化に対応するファンアウトパッケージについて、当社の技術を紹介します。

半導体実装

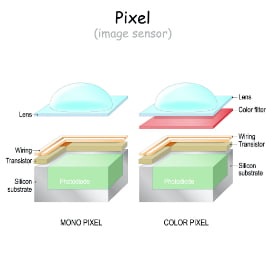

センサー

新規ポリマーを用いた高耐熱・高透明なマイクロレンズレジストの開発

医療用や車載向けのカメラにも幅広く活用されるイメージセンサー。ここには、当社の「マイクロレンズレジスト」が使用されています。

センサー

お問い合わせ・資料ダウンロード

ご要望やお困りごとがありましたらお問い合わせください。

各製品に関する資料もダウンロードいただけます。