バンプ形成用レジスト

Auバンプ/Cuピラー/マイクロバンプ等の銅,錫,ニッケル,ハンダ電解めっき用フォトバンプ形成用レジスト

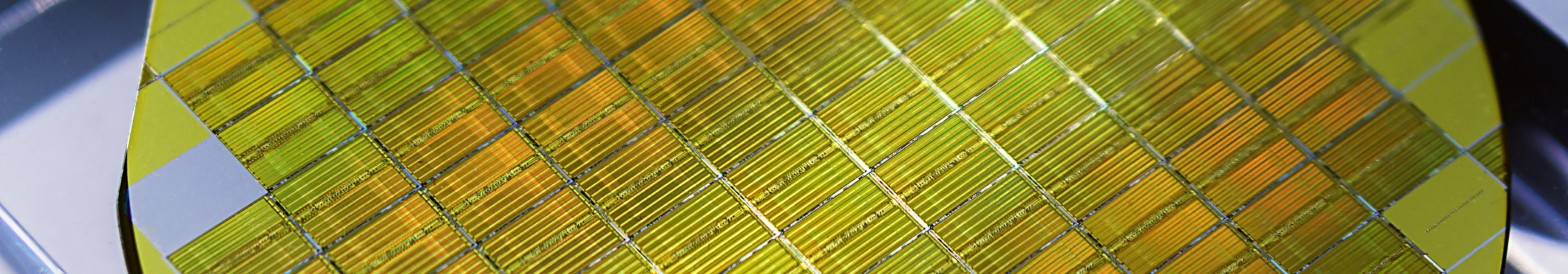

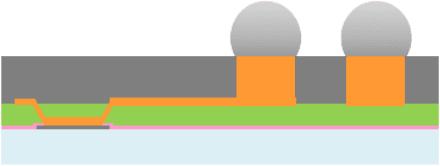

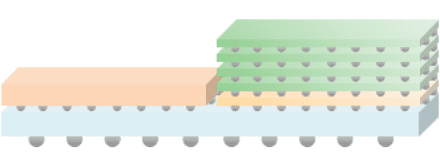

高密度半導体実装における2.5/3Dシリコン貫通電極パッケージ、TSV積層メモリー、WL-CSP ( ウエハレベルチップサイズパッケージ ) 、Cu ピラー / フィリップチップパッケージや LCDドライバーのマイクロバンプ / 金スタットバンプ / Cuポストの電極形成に用いられるノンシアン金、銀、 錫、 銅、 ニッケルの各種金属のめっき液への耐性を持った電解めっき用途の高解像ポジ型厚膜レジストです。

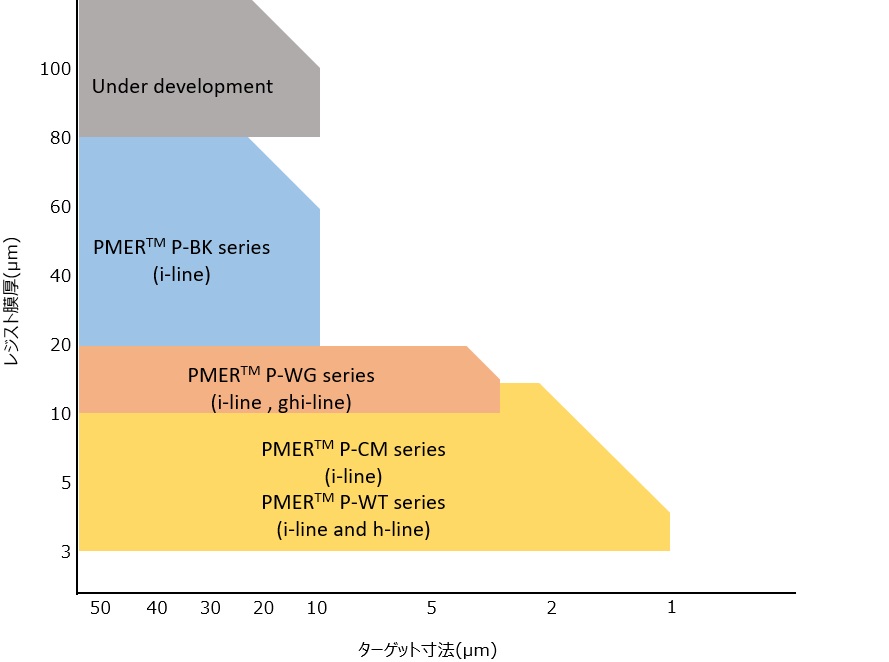

高感度にて微細なホールパターン形成が可能。下地との高密着性を有し、めっき工程で高いプロセスマージンを有しております。また、めっき工程後のレジスト膜除去では、ネガ型レジストに比べて容易に剥離が可能。バンプ電極形成工程でのコストダウンを可能にします。レジスト膜厚は10~100μmまで各膜厚に対応できるレジストを各種取り揃えております。 SiP ( System in Package ) 、PoP ( Package on Package ) などの高度な半導体実装技術に対応した各種プロセス材料をご用意しております。

関連技術情報

電解めっき用フォトレジストラインナップ

Cuピラー、マイクロバンプ向けめっき用フォトレジスト

Cuピラーバンプ、Sn/Ag バンプ、マイクロバンプ 形成

PMER P-BKシリーズ

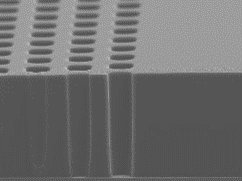

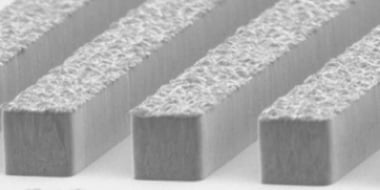

高解像性、めっき液耐性を持ち合わせためっき工程用ポジ型フォトレジストです。Cu Pillar BGAやTSVメモリーのマイクロバンプに要求される高アスペクト比のめっき電極形成工程に対応いたします。Cu、Ni、SnAgの連続めっきにも対応可能です。電解めっき工程後のレジスト剥離性も良好ですので、電極にダメージ無く容易にレジスト除去が可能です。

特長

- ポジティブトーンタイプ

- 現像:TMAH 2.38%

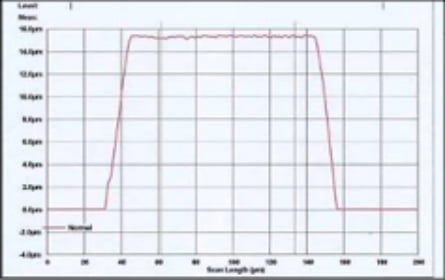

- レジスト膜厚:20μm〜65μm

- ワイドプロセスマージン&クラックマージン

- 矩形形状&良好な剥離性

条件

下地 :Cuプリベーク :145℃-300秒

露光 :i 線 ステッパー(NA:0.18)

P.E.B. :85℃-180秒

現像 :TMAH 2.38%

60秒 × 6 パドル

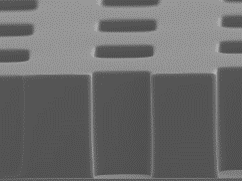

レジストプロファイル

| S/H 30μm | S/H 20μm | S/H 10μm | |

|---|---|---|---|

| レジスト膜厚 65μm |

|

|

|

PMER P-CSシリーズ

金、パラジウム等の貴金属めっき工程に使用可能。金属めっき液に対し高耐性をもつ電解めっき工程用フォトレジストです。

特長

- 微細金めっき

- ポジティブトーンタイプ

- 適用膜厚範囲=10~20μm

フォトリソ条件

下地

Au

膜厚

20μm

金めっき条件

前処理

O2 プラズマアッシング

0.15torr ,300W ,40℃-60秒

鍍金

シアン金めっき液

レジスト除去

弊社 レジスト剥離液 ST-120

Pd めっき条件

めっき液タイプ

Pdめっき液 pH = 7.5

めっき条件

1.5ASD ,50℃-48.6分

パラジュウムめっき厚

18μm

レジスト剥離

ST-120 ,45℃-10分

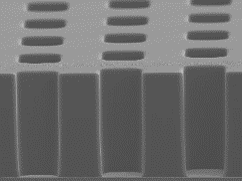

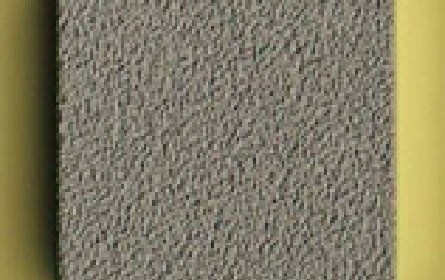

レジスト除去後 金めっき形状

| L/S=20/20μm | 20μm角柱 めっき形状 |

|---|---|

|

|

パラジウム めっき形状

お問い合わせ・資料ダウンロード

ご要望やお困りごとがありましたらお問い合わせください。

各製品に関する資料もダウンロードいただけます。